周波数拡散クロックIC編

富士通マイクロエレクトロニクスに聞く!周波数拡散クロックIC編

使う前に、選ぶ前に、これだけは知っておきたい部品のジョーシキ。

今さら聞けない あんな質問、こんな疑問を、RSが代わりに伺ってきました。

取材協力:富士通マイクロエレクトロニクス 様

取扱い製品情報 [PR]

- RS取扱い 富士通マイクロエレクトロニクス製品一覧

メモリ、電源IC、マイコン、AD/DAコンバータなど - 富士通マイクロエレクトロニクス 周波数制御IC製品一覧

タイマーIC、スペクトラム拡散クロックジェネレータほか - RS取扱い クロック発生 / タイミングデバイス製品一覧

水晶発振器、PLL、プログラマブル発振器ほか2,000点以上

元から絶つ

ノイズ規制と対策

ICなのにノイズ対策部品なんですか

電子機器が発する電磁ノイズの量は、国際的な規格でスペクトラムが規制されており、電子機器はこれをクリアするノイズ対策が必要です<図1>。周波数拡散クロックIC (Spread Spectrum Clock Generator 以下 SSCG )は、デジタル機器のシステムクロックを生成するIC<図2>ですが、クロック源をSSCGにすることでノイズの発生量を少なくできるノイズ対策部品でもあります。一般のノイズ対策はノイズの存在を前提とした言わば対症療法であり、例えばパラレルのデジタルラインでは各ライン毎、電源では各負荷端でといった具合に各所で対策を施す必要があります。これに対して、SSCGは原因療法とも言えるものでノイズの発生そのものを「源」で抑制するため、一般的なノイズ対策の部品点数を大幅に削減できるメリットがあります。

図1:CISPR22 (情報技術装置の無線妨害波特性の許容値と測定法) による許容値

図2:SSCGの製品例

拡げて下げる

スペクトラム拡散

ノイズが減る仕組みが分かりません

<図3>はデジタル機器から放射されるノイズの典型的なスペクトラム例です。細く尖ったスペクトルが等間隔に並び高い周波数まで分布していることに注目してください。これらはシステムのクロックとその高調波に起因する成分です。つまり、デジタル機器から放射されるノイズの源は主にシステムクロックであることが分かります。これに対してSSCGは尖ったスペクトルの幅を拡げ、代わりにピーク値を抑えます。実際にはクロック周波数にわずかな変動を与えます。周波数領域で線状に集中していたエネルギーを散らすのでスペクトラム拡散(Spread Spectrum)と呼ぶのが一般的ですが、クロックに周波数変調(FM)をかけていると考えることができます。<図4>には拡散によってピーク値が下がる様子を示しました。この例では±1.5%の変調でおよそ20dBもの減衰が得られています。なお、同図は基本波を測定したものですが、高調波も同時に拡散されノイズが大きく減少します。

図3:デジタル機器のノイズスペクトラム

図4:ノイズピークの低減例

フラットトップ

方式と選択

SSCGに換えるだけで効くんですか

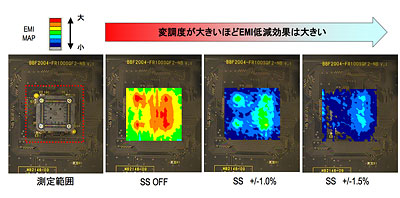

クロックのスペクトラムを拡散すればピーク値は確実に下がります。とはいえ、その下がり具合は拡散の方法、具体的には周波数変調の変調度(周波数変移)、変調波形(時間に対する周波数変化の仕方)、変調周波数などに大きく依存します。<図5>は変調度によるノイズ発生量を比較したものです。当然ながら変調度が深い(変移量が大きい)ほど大きな効果が得られています。変調波形と変調周波数に関しては、様々なものが考案されています。<図6>は変調波形が正確な三角になるようにしたうえで時間毎に周波数を位相連続で変化させる製品のスペクトラム例です。頂上部がフラットになる良好なスペクトラムが得られています。

図5:変調度によるノイズ量の違い

図6:変調波形とスペクトラムの例

一方、SSCGを使用する回路やシステム側にはクロック源としての要求仕様がありますので、それぞれのアプリケーションに適した品種の選択や機能設定が必要です。具体的選択は入力(基準クロック)と出力(逓倍率)の周波数が基本になります。複数の出力を必要とするシステムに対しては多出力のSSCGもあります。設定に関しては、変調オフの時のクロック周波数に対して上下どちら側に拡散させるかというのもそのひとつです。通常はオフ時の周波数を中心に拡散するセンタースプレッドにしますが、クロックをデバイスの最高周波数で使っている場合などは上側に拡散すると周波数限度を超えてしまうことになるため、オフ時の周波数から下方向だけに拡散するダウンスプレッドにします<図7>。

図7:周波数拡散の方向

揺らぐ想い

活用法と注意点

ジッタが増えそうで心配です

SSCGはクロックに周波数変調を施します。これを時間軸で考えるとクロックにジッタを付加することにほかなりません。そして、デジタルシステムにジッタが加わることは一般に好ましいことではありません。しかしながら、SSCGによる変調はクロック周期に対してゆっくりであるうえ周波数の変化は連続的です。結果的に付加されるのは周期ジッタ(Period jitter)が主であって、多くのデジタル回路で誤動作の原因となりやすいサイクル間ジッタ(Cycle to Cycle Jitter)の量はごくわずかです<図8>。

図8:周期ジッタ(上)とサイクル間ジッタ(下)

したがって通常のアプリケーションに対してジッタは実際上問題になりませんが、ジッタに敏感な回路には適用できないもしくは対策が必要な場合もあります。例えば、A/D変換回路に対してはFIFO(First-inn First -Out)のバッファを介することでジッタを回避する必要があります。機器間を非同期でデジタル転送をする場合なども同様です。<図9>はデバイス間に距離があり、かつ受信側にオーディオのD/Aコンバータが置かれた例です。受信側でバッファすることでバスラインからのノイズ輻射を抑えながら、ジッタによるノイズを回避し高音質を維持します。バスに使用するフレキシブル基板やケーブルなどはノイズの放射源になりやすいうえシールドなどの対策が施しにくく、ノイズフィルタでは波形が鈍ってしまうといったことがありますが、SSCGは原理的にそうした問題が発生しないこともメリットです。

図9:オーディオシステムへの適用例

取扱い製品情報 [PR]

- RS取扱い 富士通マイクロエレクトロニクス製品一覧

メモリ、電源IC、マイコン、AD/DAコンバータなど - 富士通マイクロエレクトロニクス 周波数制御IC製品一覧

タイマーIC、スペクトラム拡散クロックジェネレータほか - RS取扱い クロック発生 / タイミングデバイス製品一覧

水晶発振器、PLL、プログラマブル発振器ほか2,000点以上