Altera プログラマブルロジック開発ツール FPGA Arria V GX

- RS品番:

- 787-7037

- メーカー型番:

- DK-START-5AGXB3N

- メーカー/ブランド名:

- Altera

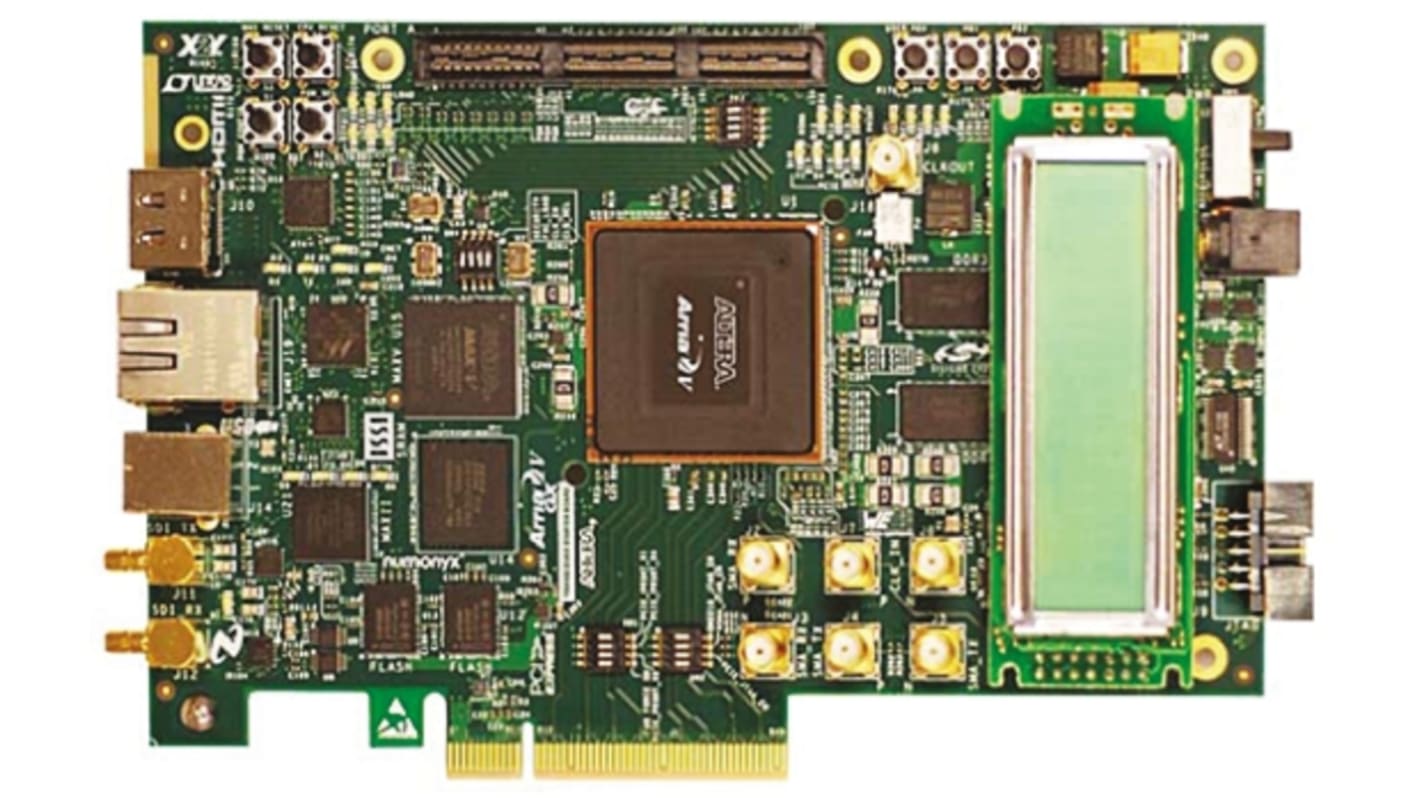

この画像は商品カテゴリーのイメージです。

取扱終了

在庫限りでお取扱いは終了致します。

- RS品番:

- 787-7037

- メーカー型番:

- DK-START-5AGXB3N

- メーカー/ブランド名:

- Altera

仕様

データシート

その他

詳細情報

製品情報(複数選択可)を選択して、類似製品を検索します。

すべて選択 | 製品情報 | 内容 |

|---|---|---|

| ブランド | Altera | |

| プログラマブルロジックテクノロジー | FPGA | |

| キットの分類 | スタータキット | |

| 対象機器 | 5AGXFB3H4F35C5N | |

| キット名 | Arria V GX | |

| すべて選択 | ||

|---|---|---|

ブランド Altera | ||

プログラマブルロジックテクノロジー FPGA | ||

キットの分類 スタータキット | ||

対象機器 5AGXFB3H4F35C5N | ||

キット名 Arria V GX | ||

Arria V GX FPGAスタータキット、Altera

Altera Arria® V GX FPGAスターターキットには、コスト重視のFPGAアプリケーションを直ちに開発するために必要なすべてのハードウェア及びソフトウェアが含まれています。 高精細マルチメディアインターフェイス(HDMI)及びシリアルデータインターフェイス(SDI)コネクタを特長としています。

FPGA

Arria V GX 5AGXFB3H4F35C5N

システムコントローラ: MAX V 5M2210ZF256C4Nデバイス

電源モニタのGUI

8チャンネルA / Dコンバータ(ADC)

非絶縁電力レール

高速パッシブパラレル(PFL)、パラレルフラッシュローダ(PFL)を使用したx16モード

コントロール及びステータスレジスタ

組み込みUSB-Blaster II: MAX II EPM570GM100C4Nデバイス

HDMI1.3 TX

XCVR x 4、2.7 Gbps (レベルシフタで最大)及び270 MHz TxクロックHDMI Txコネクタ

STMicroelectronics HDMIレベルシフタSTHDLS101T

レベルシフトXCVR PCML 1.5 V <-> TMDSレベル

DDC及びHPD <-> HDMI準拠レベル

最大2.7 Gbpsのデータチャンネル、HDMI1.3準拠

最大の270 MHzのクロックチャンネル、2.7Gbpsデータレートをサポート可能

HDMI使用: クロック期間 = 10x of UI

SDI 3G

XCVR Tx/Rxループバック

SMB コネクタ x 2 (ケーブル別売り)

最大2.97 Gbps

National Semiconductorドライバを使用 / レシーバはLMH0384SQ / LMH0303SQx

US及びEU規格に対応するため、XCVR refclkで148.5 MHz及び148.35 MHzが必要

回復したCDR周波数の微調整及びロックにVCXOを使用

HSMC

8 x XCVR、最大6.375 Gbps

PCI Express(PCIe)HIP ピン割り当てに非対応

4 x CMOS

専用Tx/Rxチャンネルを使用した8 x Tx及び9 x Rx差動インターフェイス

2 x 低電圧差動信号(LVDS)クロック入力

2 x 差動クロック出力

I2Cバス

JTAG

サポートされる最少電流: 2 A @ 3.3 V、1 A @ 12 V

xcvr refclk用専用クロックドメインSi 5338クロック発生器

BTS GUI付きHSMCループバック

SMA

XCVR Tx/Rxチャネル

LVPECLクロック入力

LVPECLクロック出力

xcvr refclk用専用クロックドメインSi 5338クロック発生器

DDR3 SDRAM

Micron MT41J64M16LA-15E DDR3 SDRAM 8M x 16 x 8

2デバイス: 2 x 16幅 = x32

Uniphy及び高性能(HP)コントローラIIを使用するBTS DDR3 SDRAM GUI

SSRAM

512 K x 36、18 Mb ISSI IS61VPS51236A

フラッシュとアドレス又はデータを共有

ユーザーIO

LCD文字表示

4 x DIPスイッチ

3 xプッシュボタン

4 x LED

構成

FPP x16モード

デュアルフラッシュ512 Mbit Numonyx PC28F512P30BF(52 MHz fMAX)

JTAGヘッダ

組み込みUSB Blaster II

CypressマイクロコントローラCY7C68013A(USB PHY 2.0)

MAX IIデバイス

イーサネット

10/100/1000 Base-T

RJ-45コネクタ、リンクステータス用オンボードLED

Marvell Ethernet PHY 88E1111

CLKINから50 MHzクロック数必要

Arria V GX 5AGXFB3H4F35C5N

システムコントローラ: MAX V 5M2210ZF256C4Nデバイス

電源モニタのGUI

8チャンネルA / Dコンバータ(ADC)

非絶縁電力レール

高速パッシブパラレル(PFL)、パラレルフラッシュローダ(PFL)を使用したx16モード

コントロール及びステータスレジスタ

組み込みUSB-Blaster II: MAX II EPM570GM100C4Nデバイス

HDMI1.3 TX

XCVR x 4、2.7 Gbps (レベルシフタで最大)及び270 MHz TxクロックHDMI Txコネクタ

STMicroelectronics HDMIレベルシフタSTHDLS101T

レベルシフトXCVR PCML 1.5 V <-> TMDSレベル

DDC及びHPD <-> HDMI準拠レベル

最大2.7 Gbpsのデータチャンネル、HDMI1.3準拠

最大の270 MHzのクロックチャンネル、2.7Gbpsデータレートをサポート可能

HDMI使用: クロック期間 = 10x of UI

SDI 3G

XCVR Tx/Rxループバック

SMB コネクタ x 2 (ケーブル別売り)

最大2.97 Gbps

National Semiconductorドライバを使用 / レシーバはLMH0384SQ / LMH0303SQx

US及びEU規格に対応するため、XCVR refclkで148.5 MHz及び148.35 MHzが必要

回復したCDR周波数の微調整及びロックにVCXOを使用

HSMC

8 x XCVR、最大6.375 Gbps

PCI Express(PCIe)HIP ピン割り当てに非対応

4 x CMOS

専用Tx/Rxチャンネルを使用した8 x Tx及び9 x Rx差動インターフェイス

2 x 低電圧差動信号(LVDS)クロック入力

2 x 差動クロック出力

I2Cバス

JTAG

サポートされる最少電流: 2 A @ 3.3 V、1 A @ 12 V

xcvr refclk用専用クロックドメインSi 5338クロック発生器

BTS GUI付きHSMCループバック

SMA

XCVR Tx/Rxチャネル

LVPECLクロック入力

LVPECLクロック出力

xcvr refclk用専用クロックドメインSi 5338クロック発生器

DDR3 SDRAM

Micron MT41J64M16LA-15E DDR3 SDRAM 8M x 16 x 8

2デバイス: 2 x 16幅 = x32

Uniphy及び高性能(HP)コントローラIIを使用するBTS DDR3 SDRAM GUI

SSRAM

512 K x 36、18 Mb ISSI IS61VPS51236A

フラッシュとアドレス又はデータを共有

ユーザーIO

LCD文字表示

4 x DIPスイッチ

3 xプッシュボタン

4 x LED

構成

FPP x16モード

デュアルフラッシュ512 Mbit Numonyx PC28F512P30BF(52 MHz fMAX)

JTAGヘッダ

組み込みUSB Blaster II

CypressマイクロコントローラCY7C68013A(USB PHY 2.0)

MAX IIデバイス

イーサネット

10/100/1000 Base-T

RJ-45コネクタ、リンクステータス用オンボードLED

Marvell Ethernet PHY 88E1111

CLKINから50 MHzクロック数必要

付属品

プバック及びデバッグヘッダドーターカード、USBケーブル、75 Ω SMBビデオケーブル、イーサネットケーブル、Quartus IIソフトウェアの開発キット版(DKE)用ライセンス(Windowsプラットフォームのみ)

FPGAは、相互接続プログラムを通じて接続された構成可能ロジックブロック(CLB)のマトリクスから構成される半導体デバイスです。 ユーザーは、SRAMをプログラムすることによりこれらの相互接続を決定します。 CLBはシンプル(AND、ORゲートなど)にも、複雑(RAMのブロック)にもできます。 FPGAでは、デバイスが基板にはんだ付けされた後でも設計に変更を加えることが可能です。