- 発行日 2023年7月21日

- 最終変更日 2024年3月25日

- 1 分

POL電源ガイド

この記事では、散らばる電源POLと分散電源のトポロジーについて解説しています。

電源はシステムのインフラ

電子機器が高機能化し回路やデバイスが高密度化するにつれ、「どのような電源をどこに配置するか」が機器のパフォーマンスを左右するようになってきました。

回路の隅々まで安定したエネルギーを供給する電源は、電子回路のインフラ(社会基盤)です。そして、インフラがシッカリと整備されていない社会からは大きな発展は望めないように、電源がシッカリしていないシステムからは優れた性能も高い信頼性も得られません。

さらに、インフラは社会の発展に合わせて進化していくべきものです。電子機器内部の電源インフラもまた、ひとつの大きな電源で全てを賄う 「集中電源」 から、複数の電源を各所に配置する 「分散電源」 へとトポロジー(接続形態)が完全に移り変わっています。

集中電源と分散電源の違い

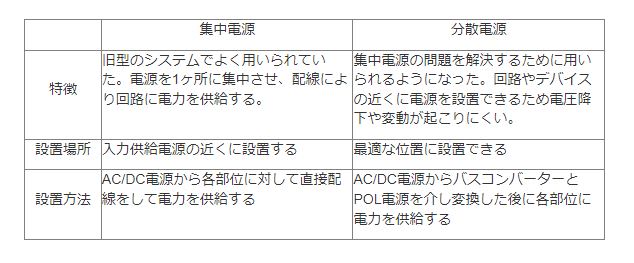

それでは、集中電源と分散電源にはどのような違いがあるのでしょうか。特徴や設置場所・設置方法について違いをお話いたします。

最近ではデバイスごとの電流への要求が高度化している傾向があり、1ヶ所に集中する電源では対処しにくくなりました。そのため、長い配線による影響が軽減される、精度の高い分散電源への必要性が高まっています。分散電源の一種であるPOL電源は、最近になり幅広い分野で使用されており、スマートフォンなどの高密度・省電力機器に適した方式であることから広く活用されています。

集中電源と分散電源の違いは、設置場所・設置方法の違いにより、効率的に電力を届けられるか否かです。

電源仕様の多様化と高度化

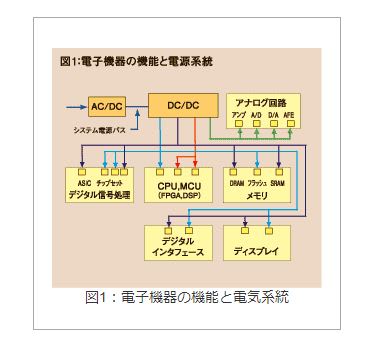

トポロジー(接続形態)の進化は、回路やデバイスが要求する仕様の多様化と高度化に起因しています。 図1は、電子機器の典型的な機能ブロックとそれらに必要な電源の供給例を示したものです。マイコン(CPU/MCU)、アナログ回路、ディスプレイなど各機能ブロックに対して電源供給が必要ですが、要求される電源電圧や精度、消費電流、要求品質などはそれぞれに異なります。

また、図2はFPGAが必要とする電源の例です。今や1個のLSIに対してさえ、何種類もの電源を供給しなければないわけです。規模は異なっても機器内の各所で多数の異なる電源供給が必要になった結果、集中電源のトポロジーは破綻しました。

集中から分散そしてPOL(Point of Load)

電源の大元は商用電源(AC100/200V)や電池などです。このため、ほとんどの電子機器では電源を何階層かに枝分かれさせて分散供給する形態が採られます。

そして、この際にポイントとなるのがPOL(Point of Load)です。POLは文字通り負荷の直近に配置する最終段階の電源です。プロセッサやFPGAに代表されるようにLSIの電源は低電圧・大電流化している上、電圧精度などは高くなる方向にあります。これに対して集中電源から長いパターンを引き回して配線したのでは要求を満足できません

そこで負荷端で電源を作り直して供給しようというのがPOLの始まりです。その後POLの概念は拡張されつつあり、負荷をLSIなど最終的な電力消費アイテムだけでなく、一枚のボードやまとまった回路まで拡張し、それらに対する電源もPOLと捉えるようになってきました。また、物理的に置かれる場所も必ずしも負荷の直近ではなく、幾つかの回路用の電源をひとまとめにして付近の回路に分配するものもPOLとして括られています。

ここにもそこにもPOL

分散電源とPOLの考え方が浸透するにつれてボード上には多数のPOLとその周辺部品が配置されることになりました。しかしながら、それらはボード上でスペースを喰いますし、数があるだけに個々のPOLが消費する電力も無視できません。したがって「適材適所のPOL配置」が最近の電源設計のポイントになっています。

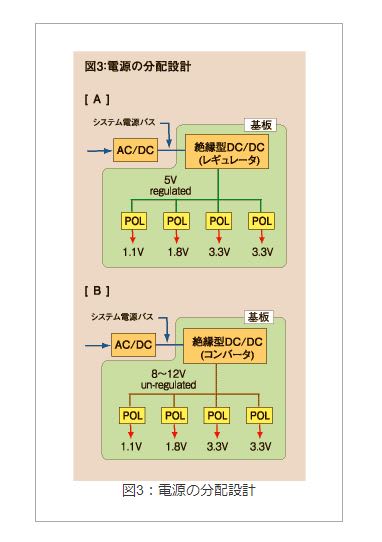

例えば図3、はAC電源を使う機器の各ボードにおける二通りの電源設計例です。どちらもボードに導かれた電源ラインを絶縁型の電源で中間電圧に変換し負荷の近くにPOLを置いています。

このとき、[A]は絶縁部を安定化機能を持った電源(レギュレータ)とし中間電圧は低めに設定されておりPOLでの消費電力が小さいのでLDO主体の場合は有利です。

一方の[B]は、絶縁電源には安定化機能を持たせずコンバータ(電圧変換器)として作用させています。コンバータはレギュレータよりも高効率が得られるため、この部分での消費電力を[A]より少なくできます。しかしながら、中間電圧は安定化されていないので、[A]よりも高めに設定する必要がありPOLの降圧比は大きくなります。

ABどちらが良いかは各負荷の条件にも左右されるため一概には言えませんが、[B]の方式が増える傾向にあります。

電源分散の構成を決めた後は、各POLにどのようなICやモジュールを使うかを考えることになります。そのとき迷うのはスイッチング電源にするかアナログのシリーズレギュレータにするかでしょう。スイッチングであれば降圧の同期整流、アナログなら小さな入出力電圧差でも動作するLDOタイプのものを選択することになります。どちらにするかは入出力の電圧差(降圧比)と電流の大きさ、回路のノイズに対する敏感さなどから判断します。

POLは回路の直近に置かれるためノイズの点からはLDOにしたいところですが、降圧比と電流が大きい負荷に対しては消費電力が大きくなるため不向きだからです。

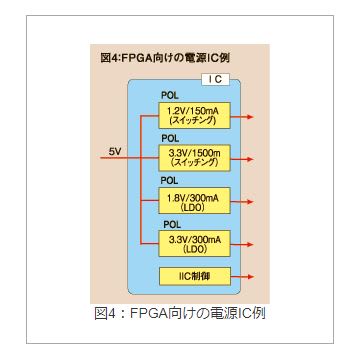

図4に、FPGA等を想定して複数のPOLをひとまとめにしたICの例を示します。消費電力(降圧比と出力電流)を考慮してスイッチングとLDOが上手く使い分けられているのが分かります。

電源管理も忘れずに

POLが各所に配置されるようになったことで、個々の回路やデバイスの電源要求を満足し電源効率も高まりました。しかしながら、ひとつのシステムに多数の電源が存在することで新たに考えなければならない問題も生じています。全体としては「電源管理」として表現される一連の項目がそれです。代表的なものとしては、各電源の立ち上がり速度と順序があります。

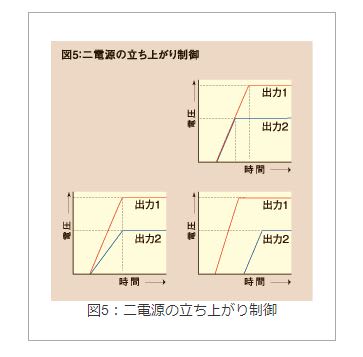

例えばアナログ回路の一部をデジタル制御で切り換えるシステムの場合、デジタルが立ち上がって初期化されてからアナログが立ち上がるようなシーケンス(動作順序)にしておかないとスイッチ切り換えが不定の状態で回路動作が始まってしまいます。この問題に対処するため最近の電源ICでは立ち上がりの制御端子が設けられており様々な立ち上がり様式を実現できます(図5)。

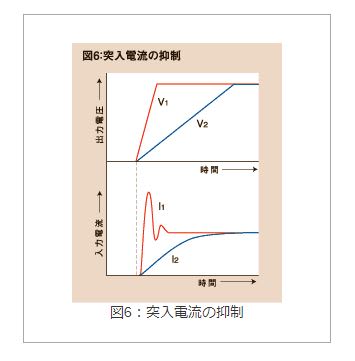

また、多数の電源が集中して立ち上がるときの突入電流にも注意が必要です。電源回路は立ち上がり時に大容量のコンデンサに充電するため、定常時に比べてはるかに大きな電流を引き込みます。この電流によって中間電圧が下がって他の電源が立ち上がれなくなるといったことも考えられます。これを回避するために大容量のPOLの立ち上がりを穏やかにする「ソフトスタート」といった配慮も必要です(図6)。